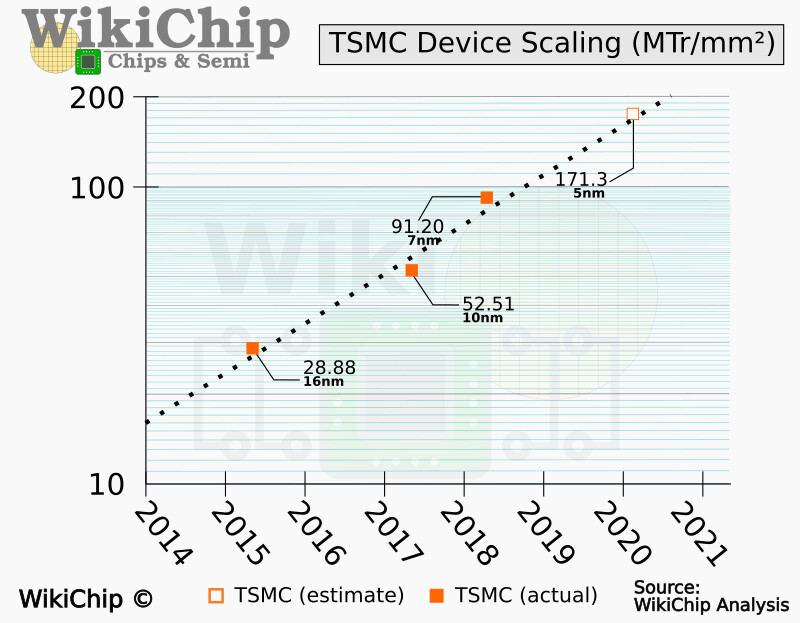

Наши коллеги с ресурса WikiChip решили проанализировать технические характеристики микросхем, которые будут производится по 5 нм техпроцессу N5P на фабриках TSMC. По предварительным оценкам микросхемы ждет значительное увеличение плотности транзисторов — аж на 84-87%, по сравнению с первым коммерческим техпроцессом 7 нм (DUV). В отчете наших коллег указано увеличение плотности транзисторов на 87%, хотя сам производитель, влице TSMC немного более скромен и прогнозирует уплотнение в 84%. Отработка и наладка 5 нм техпроцесса TSMC N5P началась в начале этого года. Объемное производство может начаться уже в апреле или мае, если график не будет сорван пандемией COVID-19.

5 нм техпроцесс обеспечивает плотность транзисторов приблизительно равную 171,3 млн. штукам на 1 мм² кристалла. Для сравнения 7 нм техпроцесс обеспечивает плотность в с 91,2 млн / мм².

Крупнейшим клиентом данных мощностей в 2020 году станет компания Apple, которая будет производить здесь процессоры серии A14.

Похожие новости из раздела:

- 5 нм мощности TSMC уже забронированы

- AMD станет крупнейшим 7 нм клиентом TSMC

- Intel ведет переговоры с TSMC о выделении 3ннм мощностей, даже несмотря на предостережения от инвестиций в Тайвань

- Генеральный директор Intel — нехватка чипов сохранится еще пару лет