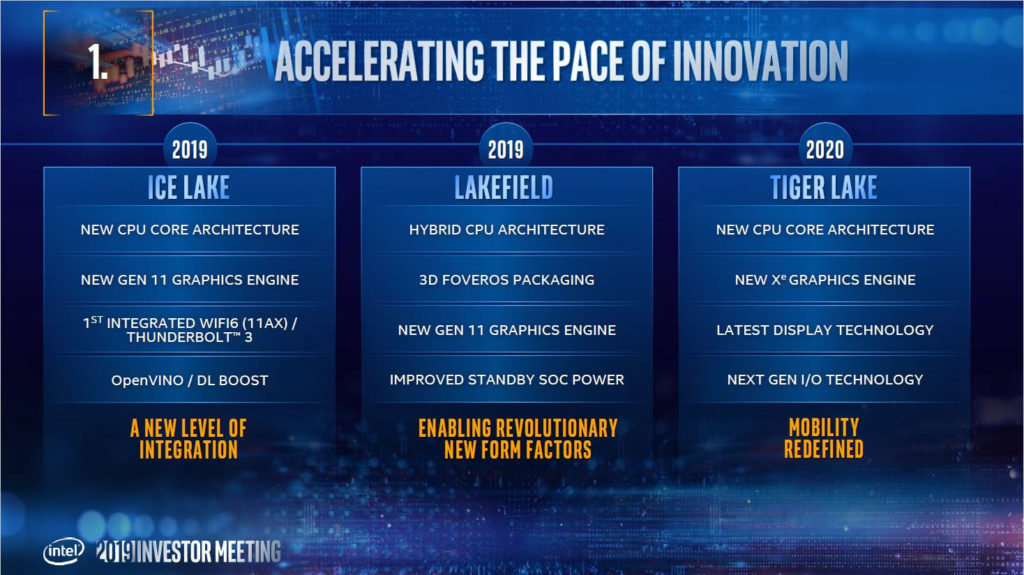

Разрабатывая нынешнюю микроархитектуру для своих процессоров под названием Skylake, компания Intel значительно перебалансировала иерархию кэша своих многоядерных процессоров. Сделано это было для того чтобы оснастить ядра процессора большим количеством быстрого кеша L2, что вынудило немного сократить объем кеша 3-го уровня (по сравнению с возможным). Такой баланс кеша используется в мобильных и настольных процессорах уже на протяжении нескольких поколений. Правда, это может измениться с выходом микроархитектуры Tiger Lake. В онлайн-базе данных Geekbench засветился прототип четырехъядерного мобильного процессора Tiger Lake-Y.

Согласно представленным данным, при условии, что Geekbench правильно читает платформу, процессор Tiger Lake-Y оснащен 4 ядрами / 8 потоками и огромным объемом кэш-памяти L2 — 1280 КБ (1,25 МБ) ядро и 12 МБ кэш-памяти L3. Intel также расширила кэш L1D до 48 КБ, а кэш L1I остался равным 32 КБ. Если говорить сухими цифрами, то размер кэша L2 увеличился на на 400%, а кэш L3 вырос на 50%!

В отличие от «Skylake-X», увеличение размера кэша L2 не стало причиной уменьшением размера общего кэша L3. Сам процессор «Tiger Lake-Y» тестировался на платформе под названием «Corktown». Ожидается, что процессоры семейства «Tiger Lake» будут выпущены в 2020–21 годах, а производиться они будут по технологии 10 нм ++ от Intel.

Похожие новости из раздела:

- Intel Ice Lake ускорятся на 40% по показателю IPC

- Процессоры Intel Tiger Lake-U получат высокую частоту

- Результаты разгона процессоров Skylake-X и Kaby Lake-X

- В сеть выложили изображение матрицы Intel «Rocket Lake-S» с аннотацией