Ожидается, что архитектура Zen6 не будет в ближайшее время для розничных и корпоративных клиентов AMD. Компания еще не представила свою архитектуру Zen5 во всех сегментах рынка, даже некоторые продукты Zen4 все ещё не выпущены (Hawk Point, M1300 и т. д.). Однако у AMD традиционно обширная дорожная карта, и предварительное планирование является одним из ключей к закреплению на различных рынках, а также помогает в конкуренции с Intel.

Революция Zen вот-вот достигнет своего шестого поколения с совершенно новым дизайном компоновки процессора с применением новых технологий для расположения компонентов CPU. По словам источников, это будет серьезный редизайн Zen5. Сообщается, что в серии ЕРУС AMD объединяет чиплеты, включающие ядра ЦП, сетевой IP и специальные FPGA. Такой подход открывает различные новые возможности и постепенно стирает различия между традиционными процессорами и специализированными ускорителями.

В сентябре мы писали о том, что Moore’s Law is Dead поделился скриншотов с презентации AMD, в которой указаны предварительные архитектурные подробности Zen5 и Zen6. Он подтвердил кодовые названия обеих архитектур как Nirvana и Morpheus. Видео в основном было посвящено Zen5, однако подробности о Zen6 подтвердили, что AMD нацелена на увеличение количества ядер на чиплет (до 32) и поддержку ускорения операций высокой точности с плавающей запятой (FP16) для ИИ и машинного обучения.

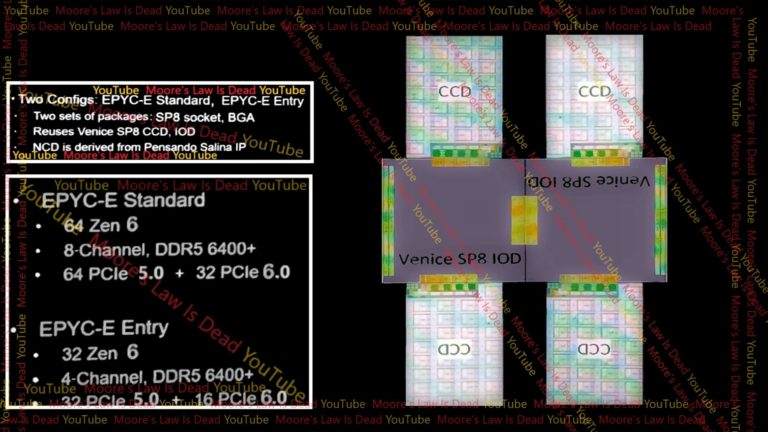

Теперь же блогер представил слайд, показывающий серию продуктов ЕРУС-Е, где Е должно означать Edge. Это означает продукт для телекоммуникационных и периферийных систем, который предназначен для использования с меньшим количества ядер и более низким энергопотреблением. На схеме показан продукт Venice SPB IOD с двумя ПЗС-матрицами с каждой стороны и 32 ядрами Zen6. В этой специальной конструкции ЦП также можно реализовать NCD (сетевые вычислительные матрицы) на основе конструкции Pensanso Salina путем замены некоторых ПЗС-матриц.

Для сравнения: разъем SPB, который будет использоваться в этой конструкции ЕРУС-Е, станет следующим разъемом ЦП для некоторых серий ЕРУС. Он будет запущен вместе с SP7, сокетом для размещения более крупных процессоров Venice. SPB — это меньший сокет, запланированный для приемников Siena и Sorano.

ЕРУС-Е будет доступен в двух вариантах: стандартная версия с 64 ядрами Zen6 или 32 ядра в варианте «Entry», Версия Standard будет иметь поддержку восьмиканальной памяти DDR5-6400 и поддержку 64 линий PCIe Gen5 и 32 линий PCle Gел6. Процессоры Entry ЕРУС-С будут иметь поддержку четырехканальной памяти DDR5-6400 и будут оснащаться 32 Geп5 и 16 Geпб линиями РСіe Gen5 и Gen6 соответственно.

Поскольку одна ПЗС-матрица имеет 32 ядра, а серия Entry EРУС-Е привязана к такому количеству ядер, это означает, что AMD может заменить одну из ПЗС-матриц своей плиткой NCD. Аналогично, в стандартной версии два чиплета Zen6 будут заменены специальными кристаллами FGPA и NCD.

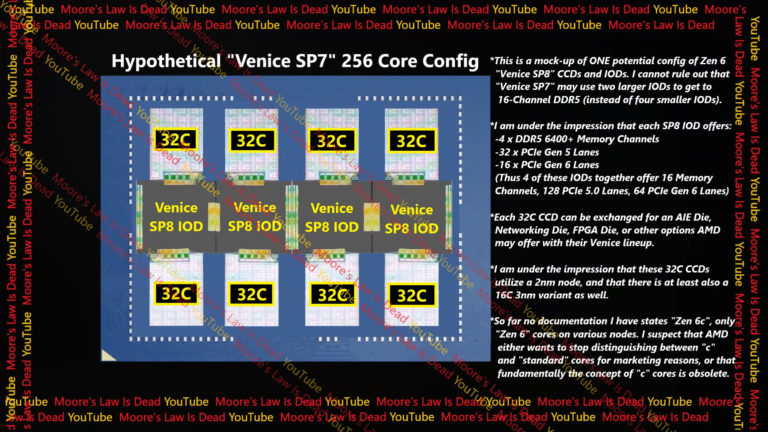

Доступ к новой документации и некоторые обоснованные предположения привели MLID к созданию макета возможного процессора Zen6 ЕРУС для сокета SP7. В настоящее время AMD не делает различия между ядрами Zen6 и предполагаемыми ядрами Zen6c (cloud/dense), что связано либо с тем, что AMD отходит от этого различия, либо с тем, что такие ядра не планируются. Несмотря на это, возможная конструкция из 8 микросхем с четырьмя кристаллами IOD может иметь до 256 ядер Zenó, что больше, чем нынешние 96 Zen4 (Genoa) или 128 Zen4c (Bergamo), а в будущем Turing будет иметь 128/192 ядер Zen5 (Classic) или Zen5 (Dense).

Похожие новости из раздела:

- AMD представляет революционные инновации для центров обработки данных с расширенной линейкой продуктов

- APU AMD Strix Point получат до 12 ядер и 24 потоков, но не будут поддерживать PCIe Gen 5.

- AMD анонсировала APU Ryzen 8000G.

- Появилась информация о микроархитектурах AMD Zen5 и Zen6.